|

研究内容 |

|

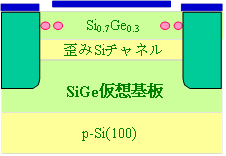

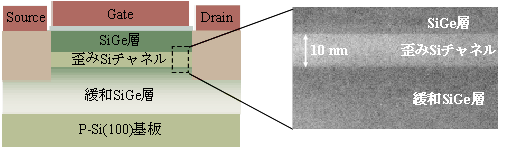

分子線エピタキシー(MBE)法を用いて半導体の積層構造を作製しています。このようにすることでトランジスタの特性を向上させることができます。下図ではSi(シリコン)層をSiGe(シリコン・ゲルマニウム)層で挟むことで歪ませ、電子をSi層に閉じ込めています。Siを歪ませると電子の散乱が抑制され、移動度が大きくなることを利用したものです。

|

|

SiGe(C)等の混晶は、IV族半導体歪みヘテロ構造を形成する際に用いられています。主として歪みSi(Ge)チャネル用の仮想基板として用いられていますが、こうした仮想基板自体の電気伝導特性についてはあまり研究が進んでいません。混晶半導体では、結晶の不完全性によって電気的性質が大きく変わり、成膜方法やその後のプロセスにも影響を受けます。当研究室ではHall測定等を用いて種々の方法で作製された仮想基板の電気伝導特性およびそのメカニズムについて研究を行っています。

|

|

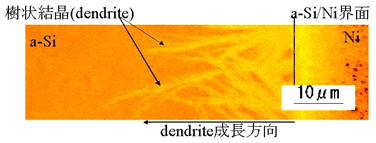

液晶ディスプレイでは、液晶分子に電界を印加して光の透過量を制御しています。この制御のためにTFT(薄膜トランジスタ)と呼ばれる小さなトランジスタが用いられています。TFTはガラス基板上に作製されるため、500℃以下の低温での工程を要求されます。このような低温プロセスで特性の良いトランジスタを作製することは極めて困難です。当研究室では種々の方法により作製した多結晶Si(Ge)薄膜及びこれを用いたトランジスタの電気伝導特性を研究しています。

|

|

IV族半導体超構造形成に関する研究 [詳細] |

|

半導体中の歪み制御に関する研究 [詳細] |

|

IV族半導体混晶の電子物性に関する研究 [詳細] |

|

ガラス基板上への多結晶Si(Ge)薄膜の形成および応用に関する研究 [詳細] |

|

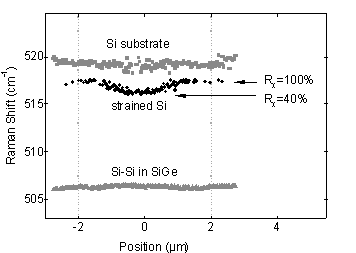

歪みSi(Ge)薄膜は、通常のSiと比較して高いキャリア移動度を得ることができるため、次世代電子デバイス用材料として注目されています。この高い移動度は歪みによる結晶格子の変形によってもたらされます。実際のデバイスでは、層間絶縁膜の存在や3次元的な素子構造を反映してチャネル層は様々な力を受けてわずかに変形します。当研究室では、格子歪みのわずかな変化が電子物性に与える影響について調べています。

|

|

4mm |

|

100nm |

|

歪みSi |